# 以 ASIC 來實現 PID 模糊控制晶片之設計

洪進華 莊宗桓 楊溢棋 劉俊麟 大葉大學電機工程學系 彰化縣大村鄉山腳路 112 號

## 摘要

本研究主要在以 ASIC (application specific integrated circuit)的設計流程來設計一個具有 PID (proportional integration derivative)功能的 Fuzzy 控制晶片,此控制晶片僅需要用到 16 個 clock cycles 就能推論完畢並輸出推論值。在當今 Fuzzy 應用多數仍以微處理機為主體來實現 Fuzzy 核心的推論運算,但受限於微處理機的工作頻率太慢,造成整體系統的效率降低,且傳輸界面易受外力環境雜訊干擾而影響穩定性。所以此應用對於需要快速推論分析的"及時系統(real time)"有相當的幫助。在此晶片中我們還提出了"數位平均值濾波"與"可調式取樣脈衝"的技術及硬體架構來執行模糊推論,此一技術能確保即使是在複雜的環境下工作,亦能避免 Fuzzy-PID 晶片在高速推論時發生錯誤動作,使外力雜訊干擾因素所導致的不正確推論情形降到最低。

**關鍵詞:**PID,模糊

# Design for Fuzzy-PID Controller Chip by Using ASIC

JIN-HUA HONG, TSUNG-HUAN CHUANG, YI-CHI YANG and CHANN-LIN LIU

Department of Electrical Engineering, Da-Yeh University

112 Shan-Jiau Rd., Da-Tsuen, Chang-Hua, Taiwan

## **ABSTRACT**

A Fuzzy-PID (proportional integration derivative) controller chip has been designed, which only requires sixteen clock cycles to finish the Fuzzy-PID operation. Due to the high clock rate and less clock numbers for Fuzzy-PID operation, our design is very suitable for real time application. In this paper, the "Digital Average Filtering" and "Tunable Sampling Clock" techniques are also proposed to avoid redundant error action and improve the stability of Fuzzy-PID systems.

Key Words: PID, fuzzy

# 一、簡介

PID 控制 (proportional integration derivative, PID) 其 特點是需耍建立受控設備 (plant) 數學模型以便對 "真實" 系統做數學抽象的近似描述,而用"精確"的形式把系統表 現出來,但常受到數學模式建構限制而產生匹配調測複雜因 素,且若受控設備因受外力干擾或長時間環境、機構變化因 素導致受控設備參數改變,控制穩定度必須重新調整而使系 統強健性受到考驗。1974年英國 E. H. Mamdani 教授, 根據 Fuzzy 理論首創者 Zadeh 教授於 1965 年所提出的"語言分 析"與"模糊推論"方法 [9], 成功應用 If-Then 形式 Rule 來敘述操作員的操控技術,並且與 Sensor 輸入資訊做近似 對照,成功的應用在自動運轉控制上,使得控制系統擺脫以 往傳統設計思維。近來利用軟體工程且採 Fuzzy 行為式控制 知識庫操作法則去取代 PID 受控設備的"精確"數學模 式,目前Fuzzy-PID雖改善增進其系統強健性,但面對現今 更複雜受控設備與需高速"即時處理"系統應用上,受限於 微處理機工作頻率下其 Fuzzy 推論速度提昇有限, 所以目前 已有研究改採硬體設計 (FPGA)的方式來完成 Fuzzy-PID [3-6], 在此研究中我們更進一步以 ASIC 設計流程來實現 Fuzzy-PID 系統,以獲得更高速的 Fuzzy 推論並加入"可調 式取樣脈衝"與"數位平均值濾波"的功能來完成一個簡 易智慧型的 Fuzzy-PID 系統。

## 二、Fuzzy-PID 動作分析

## (一) PID 架構

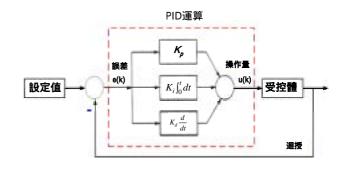

傳統 PID 控制基本架構如圖 1 所示 [1],採用閉回路迴 授信號控制架構 (closed loop feed-back control),從受控設備檢測出回授信號與目標值 (desired value)做比較,然後進行調節受控設備而產生適當操作量,當受控設備受到外來的變化干擾,系統會自行控制以恢復趨近目標值。因此 PID 有賴於精確的系統數學模式,透過時域-頻率分析方式,找出適當的控制演算公式所需的工作參數 (Kp、Ki、Kd),若選擇不適當或當受控設備參數變動時,容易造成系統不穩定。

類比 PID 演算公式:

$$u(t) = K_p e(t) + K_I \int_0^t e(t)dt + K_d \frac{de}{dt}$$

(1)

圖 1. PID 基本架構

數位 PID 演算公式:

$$u(n) = K_p e(n) + K_I T \sum_{k=0}^{n} e(k) + \frac{K_d}{T} [e(n) - e(n-1)]$$

(2)

然而 Fuzzy 控制只需將受控設備傳來的信號經模糊化 (fuzzification)處理,經由所定義的經驗法則及決策流程組成之知識庫推論分析後,結果經解模糊化 (defuzzification)後傳至受控設備進行控制,由於推論過程中不需受控設備數學模式即可運作,因此避免了 PID 在非線性時所造成不穩定現象。

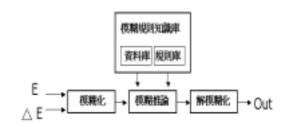

## (二)模糊演算流程

Fuzzy 基本架構如圖 2 所示,受控設備所涉及的領域知識(domain knowledge)和操控目標的資訊量,主要是由資料庫(data base)及規則庫(rule base)組成,資料庫存放領域知識的 Fuzzy 歸屬函數,規則庫則存放 Fuzzy 蘊含式(fuzzy implication)。蘊含式以下列式子(3)來表示,其中If 部份的 *E* is *MFei* and *E* is *MFQi* 稱為前導命題(antecedent proposition),提供判別語句成立條件依據。而Then 部份的 *Z* is *Ri* 稱為後導命題(consequent proposition),提供執行符合條件的結果。

Fuzzy 蘊含式:

**■** 2. Fuzzy 基本架構

Rulei: If E is MFei and E is MFQi Then Z is Ri, (3) 其中 i 為語句的編號。

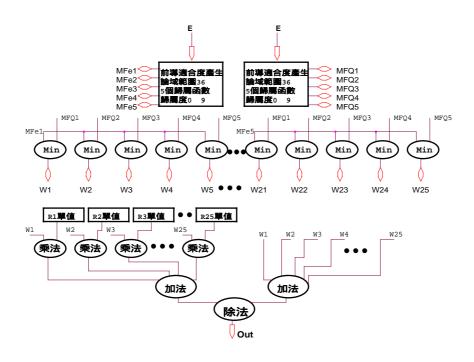

#### (三)模仿 PID 動作之 Fuzzy 演算

在考量硬體面積及速度因素下,我們使用後導命題模糊單值簡化型態(simplified fuzzy-singleton)之推論方式路[7,8],其求取前導適合度的方式與Mamdani MAX-MIN相符,但簡化了後導適合度推論,以指定模糊單值實數直接代入推論輸出函數運算,以二個輸入一個輸出演算流程如下:

Rule1: If E is MFe1 and E is MFQ1 Then Z is R1 Rule2: If E is MFe2 and E is MFQ2 Then Z is R2

Rule3: If E is MFe3 and E is MFQ3 Then Z is R3

## 其中 E 為誤差值 E 為誤差變化量

1. 計算出每條 Rule 的前導適合度:

$WI = \mu MFeI(E) \wedge \mu MFQI(E)$

$W2 = \mu MFe2(E) \wedge \mu MFQ2(E)$

$W3 = \mu MFe3(E) \wedge \mu MFQ3(E)$

^:表示取小值符號, µ:表示歸屬度

2. 前導適合度產生後,後導適合度模糊單值, RI、R2、R3 直接代入解模糊化推論函數:

$$Out = \frac{W1*R1 + W2*R2 + W3*R3}{W1 + W2 + W3}$$

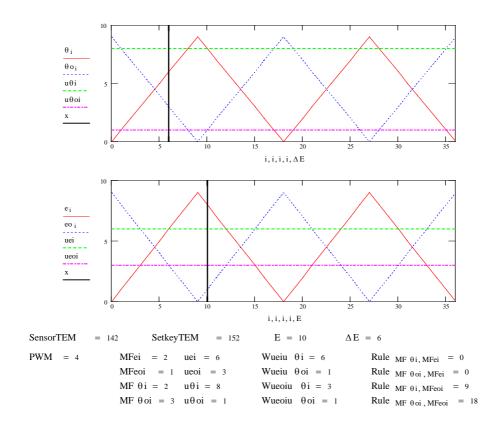

依循以上所列,應用於以下 Fuzzy 範列規格時流程如圖 3 所示,使用 MathCAD 分析模擬推論結果如圖 4 所示:

- 1. 歸屬函數共有5個且為等腰三角型表示。

- 2. 二變數 E 與 E , 蘊含式共有 25 個單值。

- 3. 輸入與輸出的論域範圍設定為 36 個值。

- 4. 歸屬度由 0 9分別表 0 1狀態。

# 三、電路架構與實現

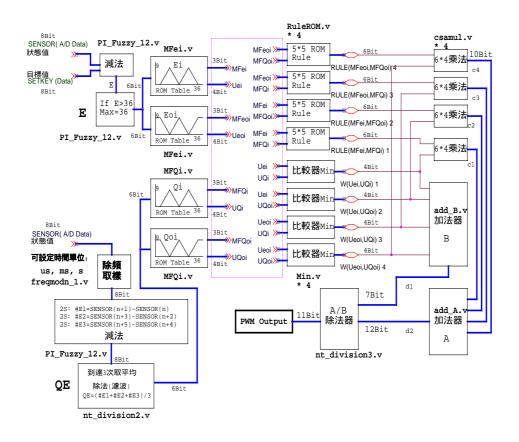

在本文中,我們以 Verilog 硬體電路描述語言來架構整個 Fuzzy-PID 的電路, Verilog 硬體電路描述語言提供一個用來描述電路狀態、行為模式、Gate level 等工業標準化軟體格式,實現具有"可讀性(readability)"、"簡單化(simplicity)"、"可攜性(portability)"、"可重覆使用(reusability)"、"可調校性(reconfigurability)"之 RTL Code設計。可讓使用者加快產品的設計週期,並使設計之電路容易維護與修改。此 Fuzzy-PID 控制晶片共由 10 個單獨的小模組組成,依各自所處理的電路特性不同,內含狀態機、行為模式、組合邏輯等,共同整合成 PI\_fuzzy\_12.v 主程式執行 Fuzzy-PID 推論。其電路架構如圖 5 所示,MFQi.v 模組與 MFei.v 模組以 ROM 型態儲存等腰三角形歸屬函數,並執行輸入量化模糊功能。RuleROM.v 模組儲存 Fuzzy 知識庫控制規則與比較器 Min.v 模組共同組合執行模糊推論界

■ 3. Fuzzy 推論流程圖

## 大葉學報 第十二卷 第一期 民國九十二年

## 圖 4. Fuzzy 模擬推論圖

■ 5. Fuzzy-PID 電路架構

面,解模糊化界面執行由 csamul.v 乘法器 add\_A.v 加法器、add\_B.v 加法器、nt\_division3.v 除法器模組共同組成以加權平均法執行解模糊化動作。"可調式取樣脈衝"的功能由freqmodn\_1.v 模組執行除頻取樣來實現,其單位時間可由外部 I/O 選擇設定使用微秒(us )毫秒(ms )秒(s )為了增進 Fuzzy-PID 的穩定性,我們額外增加"數位平均值濾波"的電路,以三次誤差變化量的總合,取其平均值,並搭配"可調式取樣脈衝"的電路來執行模糊化,此界面由PI\_Fuzzy\_12.v 模組中的除頻取樣模組與 nt\_division2.v 除法器模組共同組成。此額外增加的界面能確保即使是在複雜的環境下,亦能使 Fuzzy-PID 在高速推論時避免誤動作,使因外力干擾因素產生的不正確推論降低。

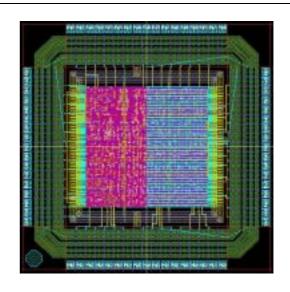

在設計過程中,我們以 Synopsys 軟體來合成 Verilog Code,使其轉換為 Gate level 的 Verilog Code,然後再以 Cadance 的 Silicon Ensemble 軟體進行自動佈局繞線,最後 再由 Timemill 軟體進行電路的時序驗証,其 layout 圖如圖 6 所示,本晶片已通過 CIC 國家晶片設計中心審查並下線製作 IC。

■ 6. Fuzzy-PID layout

# 四、模擬結果

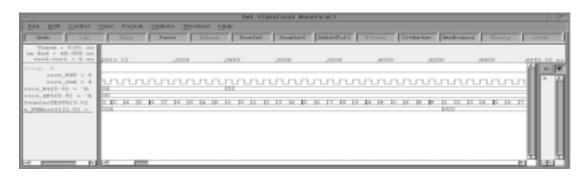

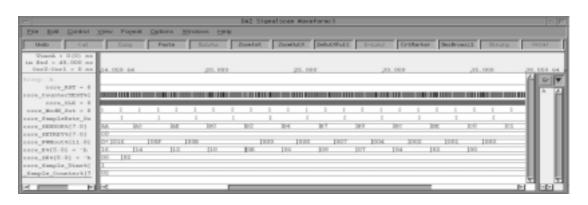

模擬結果如圖 7、圖 8 所示, clock 週期設定為 50nS, 當輸入信號 E 從 24 (十六進位) 變為 22 時, Fuzzy 晶片推論輸出信號 PWMout 從 24 轉換成 22 最新推論值共花費約 0.8uS 工作時間,符合所預期的推論速度規格。另外模仿 PID

■ 7. Fuzzy 推論之 Clock Time

■ 8. Fuzzy-PID 推論模擬圖

動作之 Fuzzy 控制狀態響應過程可從圖 8 模擬圖看出,我們將目標值 SETKEX( 8bit )設定成 CO,而感測值 SENSOR( 8bit )從 9C 開始慢慢增大,當誤差 E 愈來愈小時,送至受控體的操作量 PWMout 也隨著調整而變小,此時感測值漸漸趨近於目標值,最後推論出輸出 PWMout 等於零。

此外晶片內部的除頻器可供外部接腳信號 Sample\_Time [1:0]設定3種工作單位us、ms、s,接腳 信號Sample\_Counter[7:0]則提供彈性設定計數值。

# 五、結論

本研究我們採用 PID 的響應運作物理行為模式,轉換 敘述成為 Fuzzy 知識庫,不需受控設備數學模式路 [8],所 以僅需要較少的硬體面積,且以 ASIC 的製作流程來實現此 晶片,使系統運作速度也大大提昇。再結合我們所提出的 "可調式取樣脈衝" 與 "數位平均值濾波"的技術,則更能 增進此晶片的效能和穩定性。目前此晶片 Fuzzy 知識庫以 ROM 儲存 Rule 規範,未來若以 RAM 或是 FLASH ROM 配合運用增加其它人工智慧演算(如:遺傳基因演算法),使 其自動追尋可調取樣時間與自我隨機適應環境彈性調整知 識庫,則更能增加 Fuzzy-PID 晶片智慧性的快速響應與目標的準確度。

# 參考文獻

- 1. 孫宗瀛、楊英魁(民83), Fuzzy 控制:理論、實作與應用,全華出版社。

- 2. 陳聖凱、李祖聖(民87),以 FPGA 為基礎之模糊滑動模式控制器之 ASIC 設計,國立成功大學電機工程所碩士論文。

- 3. 許晨聲、李祖聖(民87),以 FPGA 實現動態模糊控制器 IC 之設計,國立成功大學電機工程所碩士論文。

- 4. 雷景期、陳榮順(民 88), CPLD 控制晶片在自動倒車 上之設計與實作,國立清華大學動力機械工程所碩士論 文。

- 5. 楊溢棋(民91),以 FPGA 實現 PID 模糊控制晶片之設計,大葉大學電機工程所碩士論文。

- 6. 蘇裕記、李祖聖(民88),以 FPGA 晶片實現智慧型車庫停車控制系統,國立成功大學電機工程所碩士論文。

- Hu, B. S. and J. Li (1996) The fuzzy PID gain conditioner: algorithm, architecture and FPGA implementation. *IEEE International conference on Industrial Technology*, 2-6, 621-624.

- 8. Ichihashi, H. and T. Watanabe (1990) Learning control by fuzzy models using a simplified fuzzy reasoning. *Journal of Japan Society for Fuzzy Theory and Systems*, 2, 429-437.

- Zadeh, L. A. (1965) Fuzzy sets. *Information and Control*, 8, 338-353.

收件: 91.07.10 修正: 91.09.25 接受: 91.10.11